### LM8272 Dual **RRIO, High Output Current & Unlimited Cap Load Op** Amp in Miniature Package **General Description** Features

The LM8272 is a Rail-to-Rail input and output Op Amp which can operate with a wide supply voltage range. This device has high output current drive, greater than Rail-to-Rail input common mode voltage range, unlimited capacitive load drive capability while requiring only 0.95mA/channel supply current. It is specifically designed to handle the requirements of flat panel TFT panel  $V_{COM}$  driver applications as well as being suitable for other low power, and medium speed applications which require ease of use and enhanced performance over existing devices.

Greater than Rail-to-Rail input common mode voltage range with 50dB of Common Mode Rejection, allows high side and low side sensing, among many applications, without having any concerns over exceeding the range and no compromise in accuracy. Exceptionally wide operating supply voltage range of 2.5V to 24V alleviates any concerns over functionality under extreme conditions and offers flexibility of use in multitude of applications. In addition, most device parameters are insensitive to power supply variations; this design enhancement is yet another step in simplifying its usage.

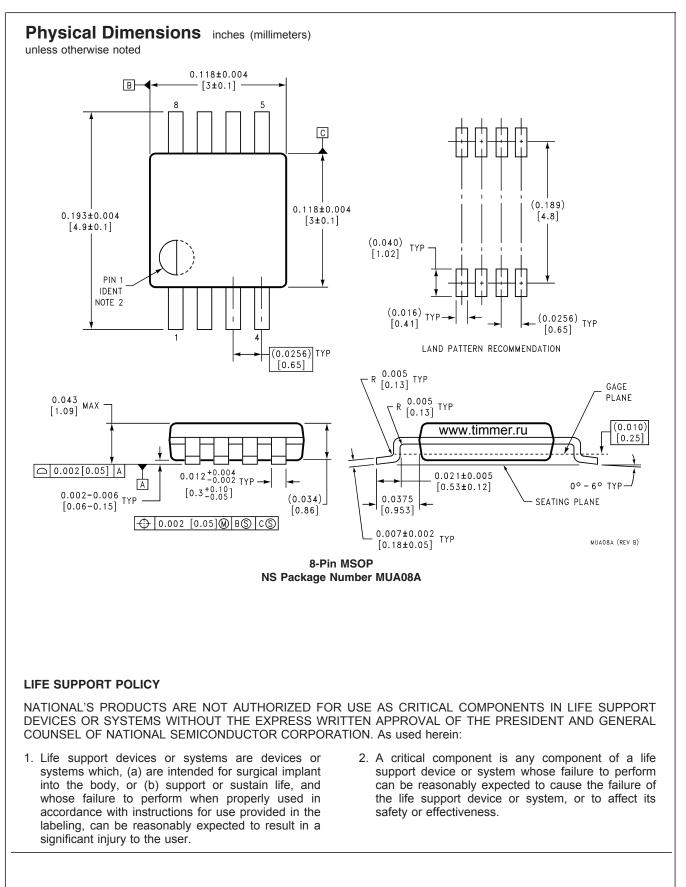

The LM8272 is offered in the 8-pin MSOP package.

(V<sub>S</sub> = 12V, T<sub>A</sub> = 25°C, Typical values unless specified).

| ■ GBWP                                             | 15MHz             |

|----------------------------------------------------|-------------------|

| Wide supply voltage range                          | 2.5V to 24V       |

| Slew rate                                          | 15V/µs            |

| Supply current/channel                             | 0.95mA            |

| Cap load tolerance                                 | Unlimited         |

| <ul> <li>Output short circuit current</li> </ul>   | ±130mA            |

| <ul> <li>Output current (1V from rails)</li> </ul> | ±65mA             |

| Input common mode voltage                          | 0.3V beyond rails |

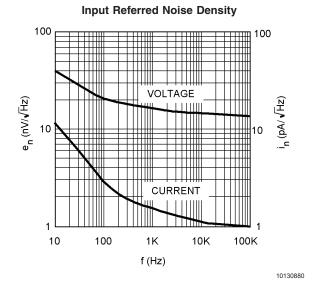

| Input voltage noise                                | 15nV/ √Hz         |

| Input current noise                                | 1.4pA/ √Hz        |

### Applications

- TFT-LCD flat panel V<sub>COM</sub> driver

- A/D converter buffer

- High side/low side sensing

- Headphone amplifier

### **Ordering Information**

| 8-Pin MSOP | LM8272MM | A60 | 1k Unit Tape and Reel   | MUA08A   |

|------------|----------|-----|-------------------------|----------|

| L          | M8272MMX | AOU | 3.5k Unit Tape and Reel | INIUAUOA |

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance                                     | 2KV (Note 2)                               |

|---------------------------------------------------|--------------------------------------------|

|                                                   | 200V(Note 9)                               |

| V <sub>IN</sub> Differential                      | +/-10V                                     |

| Output Short Circuit Duration                     | (Notes 3, 11)                              |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | 27V                                        |

| Voltage at Input/Output pins                      | V <sup>+</sup> +0.3V, V <sup>-</sup> -0.3V |

| Storage Temperature Range                         | -65°C to +150°C                            |

|                                                   |                                            |

**5V Electrical Characteristics**

| Junction Temperature (Note 4)    | +150°C |

|----------------------------------|--------|

| Soldering Information:           |        |

| Infrared or Convection (20 sec.) | 235°C  |

| Wave Soldering (10 sec.)         | 260°C  |

### **Operating Ratings**

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> )   | 2.5V to 24V    |  |  |  |

|-----------------------------------------------------|----------------|--|--|--|

| Junction Temperature Range(Note 4)                  | -40°C to +85°C |  |  |  |

| Package Thermal Resistance, $\theta_{JA}$ ,(Note 4) |                |  |  |  |

| 8-Pin MSOP                                          | 235C/W         |  |  |  |

# Unless otherwise specified, all limited guaranteed for $T_J = 25^{\circ}C$ , $V^+ = 5V$ , $V^- = 0V$ , $V_{CM} = 0.5V$ , $V_O = V^+/2$ , and $R_L > 1M\Omega$ to $V^-$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                             | Condition                                                                             | Typ<br>(Note 5) | Limit<br>(Note 6) | Units      |

|--------------------|---------------------------------------|---------------------------------------------------------------------------------------|-----------------|-------------------|------------|

| Vos                | Input Offset Voltage                  | $V_{CM} = 0.5V \& V_{CM} = 4.5V$                                                      | +/-0.7          | +/-5              | mV         |

|                    |                                       |                                                                                       |                 | +/- 7             | max        |

| TC V <sub>OS</sub> | Input Offset Average Drift            | $V_{CM} = 0.5V \& V_{CM} = 4.5V$<br>(Note 12)                                         | +/-2            | _                 | µV/°C      |

| I <sub>B</sub>     | Input Bias Current                    | (Note 7)                                                                              | _               | ±2.00             | μA         |

|                    |                                       |                                                                                       |                 | ±2.70             | max        |

| l <sub>os</sub>    | Input Offset Current                  |                                                                                       | 20              | 250               | nA         |

|                    |                                       |                                                                                       |                 | 400               | max        |

| CMRR               | Common Mode Rejection Ratio           | $V_{\rm CM}$ stepped from 0V to 5V                                                    | 80              | 64                | dB         |

|                    |                                       |                                                                                       |                 | 61                | min        |

| +PSRR              | Positive Power Supply Rejection Ratio | V <sup>+</sup> from 4.5V to 13V                                                       | 100             | 78                | dB         |

|                    |                                       |                                                                                       |                 | 74                | min        |

| CMVR               | Input Common-Mode Voltage Range       | CMRR > 50dB                                                                           | -0.3            | -0.1              | V          |

|                    |                                       |                                                                                       |                 | 0.0               | max        |

|                    |                                       |                                                                                       | 5.3             | 5.1               | V          |

|                    |                                       |                                                                                       |                 | 5.0               | min        |

| A <sub>VOL</sub>   | Large Signal Voltage Gain             | $V_{\rm O} = 0.5$ to 4.5V,                                                            | 80              | 64                | dB         |

|                    |                                       | $R_{\rm L} = 10k\Omega \text{ to } V^+/2$                                             | 4.00            | 60                | min        |

| Vo                 | Output Swing                          | $R_L = 10k\Omega$ to V <sup>-</sup>                                                   | 4.93            | 4.85              | V          |

|                    | High                                  | $I_{SOURCE} = 5mA$                                                                    | 4.85            | 4.70              | min        |

|                    | Output Swing                          | $R_{L} = 10k\Omega$ to V <sup>+</sup>                                                 | 215             | 250               | mV         |

|                    | Low                                   | I <sub>SINK</sub> = 5mA                                                               | 300             | 350               | max        |

| I <sub>SC</sub>    | Output Short Circuit Current          | Sourcing to V <sup>-</sup><br>V <sub>ID</sub> = 200mV (Note 10)                       | 100             | —                 | mA         |

|                    |                                       | Sinking to V <sup>+</sup><br>V <sub>ID</sub> = -200mV (Note 10)                       | 100             | _                 |            |

| Ι <sub>ουτ</sub>   | Output Current                        | $V_{ID} = \pm 200 \text{mV}, V_O = 1 \text{V}$ from rails                             | ±55             | _                 | mA         |

| Is                 | Supply Current (Both Channel)         | No load, $V_{CM} = 0.5V$                                                              | 1.8             | 2.3               | mA         |

|                    |                                       |                                                                                       |                 | 2.8               | max        |

| SR                 | Slew Rate (Note 8)                    | $A_{V} = +1, V_{I} = 5V_{PP}$                                                         | 12              |                   | V/µs       |

| f <sub>u</sub>     | Unity Gain Frequency                  | $V_{I}$ = 10mVp, $R_{L}$ = 2K $\Omega$ to V <sup>+</sup> /2                           | 7.5             |                   | MHz        |

| GBWP               | Gain-Bandwidth Product                | f = 50KHz                                                                             | 13              |                   | MHz        |

| Phi <sub>m</sub>   | Phase Margin                          | $V_{\rm I} = 10 {\rm mVp}, {\rm R}_{\rm L} = 2 {\rm k} \Omega {\rm to} {\rm V}^{+}/2$ | 55              | _                 | deg        |

| e <sub>n</sub>     | Input-Referred Voltage Noise          | $f = 2KHz, R_s = 50\Omega$                                                            | 15              | —                 | nV/<br>√H: |

| Symbol             | Parameter                                                                                                                                    | Condition                                                                                    | Typ<br>(Note 5)                       | Limit<br>(Note 6)     | Units      |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|------------|

| n                  | Input-Referred Current Noise                                                                                                                 | f = 2KHz                                                                                     | 1.4                                   | _                     | pA/<br>√Hz |

| f <sub>max</sub>   | Full Power Bandwidth                                                                                                                         | $Z_{L} = (20 \text{pF}    10 \text{k}\Omega) \text{ to } \text{V}^{+}/2$                     | 700                                   | —                     | KHz        |

| Unless of          | Electrical Characteristics<br>therwise specified, all limited guaranteed f<br>$\Omega$ to V <sup>-</sup> . Boldface limits apply at the temp |                                                                                              | = 6V, V <sub>O</sub> = 6 <sup>1</sup> | V, and                |            |

| Symbol             | Parameter                                                                                                                                    | Condition                                                                                    | Typ<br>(Note 5)                       | Limit<br>(Note 6)     | Units      |

| V <sub>os</sub>    | Input Offset Voltage                                                                                                                         | V <sub>CM</sub> = 0.5V & V <sub>CM</sub> = 11.5V                                             | +/-0.7                                | +/-7<br>+/- 9         | mV<br>max  |

| TC V <sub>os</sub> | Input Offset Average Drift                                                                                                                   | V <sub>CM</sub> = 0.5V & V <sub>CM</sub> = 11.5V<br>(Note 12)                                | +/-2                                  | _                     | µV/°C      |

| в                  | Input Bias Current                                                                                                                           | (Note 7)                                                                                     | -                                     | ±2.00<br><b>±2.80</b> | μA<br>max  |

| l <sub>os</sub>    | Input Offset Current                                                                                                                         |                                                                                              | 30                                    | 275<br><b>550</b>     | nA<br>max  |

| CMRR               | Common Mode Rejection Ratio                                                                                                                  | $V_{\rm CM}$ stepped from 0V to 12V                                                          | 88                                    | 74<br><b>72</b>       | dB<br>min  |

| +PSRR              | Positive Power Supply Rejection Ratio                                                                                                        | V <sup>+</sup> from 4.5V to 13V, V <sub>CM</sub> = 0.5V                                      | 100                                   | 78<br><b>74</b>       | dB<br>min  |

| -PSRR              | Negative Power Supply Rejection<br>Ratio                                                                                                     |                                                                                              | 85                                    | _                     | dB         |

| CMVR               | Input Common-Mode Voltage Range                                                                                                              | CMRR > 50dB                                                                                  | -0.3                                  | -0.1<br><b>0</b>      | V<br>max   |

|                    |                                                                                                                                              |                                                                                              | 12.3                                  | 12.1<br><b>12.0</b>   | V<br>min   |

| A <sub>VOL</sub>   | Large Signal Voltage Gain                                                                                                                    | $V_{O} = 1V$ to 11V<br>R <sub>L</sub> = 10k $\Omega$ to V <sup>+</sup> /2                    | 83                                    | 74<br><b>70</b>       | dB<br>min  |

| Vo                 | Output Swing<br>High                                                                                                                         | $R_L$ 10kΩ to V <sup>+</sup> /2<br>I <sub>SOURCE</sub> = 5mA                                 | 11.8<br>11.6                          | 11.7<br>11.5          | V<br>min   |

|                    | Output Swing                                                                                                                                 | $R_L = 10k\Omega$ to V <sup>+</sup> /2                                                       | 0.25                                  | 0.3                   | V          |

|                    | Low                                                                                                                                          | I <sub>SINK</sub> = 5mA                                                                      | .40                                   | .45                   | max        |

| I <sub>SC</sub>    | Output Short Circuit Current                                                                                                                 | Sourcing to V <sup>-</sup><br>V <sub>ID</sub> = 200mV (Note 10)<br>Sinking to V <sup>+</sup> | 130                                   | 110<br>110            | mA<br>min  |

|                    | 1                                                                                                                                            | -                                                                                            | 1                                     | 1                     |            |

$V_{ID}$  = 200mV (Note 10)

No load,  $V_{CM}$  = 0.5V

$A_V = +1, f = 100 KHz$

f = 50 KHz

$V_{ID}$  = ±200mV,  $V_O$  = 1V from rails

$A_V = +1, V_I = 10V_{PP}, C_L = 10pF$

$A_V = +1, V_I = 10V_{PP}, C_L = 0.1\mu F$

$V_1 = 10 \text{mVp}, R_1 = 2 \text{k}\Omega \text{ to } V^+/2$

$V_1 = 10 \text{mVp}, R_1 = 2 \text{k}\Omega \text{ to } V^+/2$

$V_{I}$  = 10mVp,  $R_{L}$  = 2k $\Omega$  to V<sup>+</sup>/2

**Output Current**

Slew Rate

Phase Margin

Gain Margin

(Note 8)

Supply Current (Both Channel)

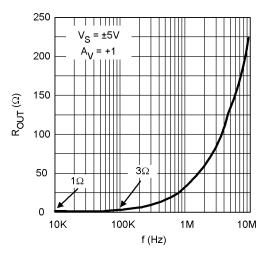

Close Loop Output Resistance

Unity Gain Frequency

Gain-Bandwidth Product

I<sub>OUT</sub>

$I_{S}$

SR

$\mathsf{R}_{\mathsf{OUT}}$

GBWP

Phim

GΜ

$f_u$

±65

1.9

15

1

3

8

15

57

20

\_

2.4

2.9

\_\_\_\_

\_

\_

\_\_\_\_

—

\_\_\_

\_

mΑ

mΑ

max

V/µs

Ω

MHz

MHz

Deg

dB

LM8272 Dual

### 12V Electrical Characteristics (Continued)

Unless otherwise specified, all limited guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = 12V$ ,  $V^- = 0V$ ,  $V_{CM} = 6V$ ,  $V_O = 6V$ , and  $R_L > 1M\Omega$  to  $V^-$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                        | Condition                                                  | Typ<br>(Note 5) | Limit<br>(Note 6) | Units      |

|------------------|----------------------------------|------------------------------------------------------------|-----------------|-------------------|------------|

| -3dB BW          | Small Signal -3db Bandwidth      | $A_V = +1, R_L = 2k\Omega$ to V <sup>+</sup> /2            | 12.5            | _                 |            |

|                  |                                  | $A_V = +1, R_L = 600\Omega$ to V <sup>+</sup> /2           | 10.5            | —                 | MHz        |

|                  |                                  | $A_V$ = +10, $R_L$ = 600 $\Omega$ to V <sup>+</sup> /2     | 1.0             | _                 |            |

| e <sub>n</sub>   | Input-Referred Voltage Noise     | $f = 2KHz, R_S = 50\Omega$                                 | 15              | _                 | nV/<br>√Hz |

| i <sub>n</sub>   | Input-Referred Current Noise     | f = 2KHz                                                   | 1.4             | _                 | pA/<br>√Hz |

| f <sub>max</sub> | Full Power Bandwidth             | $Z_{L}$ = (20pF    10k $\Omega$ ) to V <sup>+</sup> /2     | 300             | _                 | KHz        |

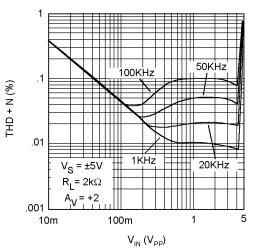

| THD+N            | Total Harmonic Distortion +Noise | $A_V = +2, R_L = 2k\Omega$ to V <sup>+</sup> /2            | 0.02            | _                 | %          |

|                  |                                  | $V_{O} = 8V_{PP}, V_{S} = \pm 5V$                          |                 |                   |            |

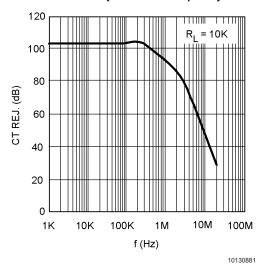

| CT Rej.          | Cross-Talk Rejection             | f = 5MHz, Driver $R_L$ = 10k $\Omega$ to V <sup>+</sup> /2 | 68              | _                 | dB         |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Rating indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics. Note 2: Human body model, 1.5kΩ in series with 100pF.

Note 3: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

Note 4: The maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_J(max) - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

Note 5: Typical Values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Positive current corresponds to current flowing into the device.

Note 8: Slew rate is the slower of the rising and falling slew rates. Connected as a Voltage Follower.

Note 9: Machine Model,  $0\Omega$  is series with 200pF.

Note 10: Short circuit test is a momentary test. See Note 11.

Note 11: Output short circuit duration is infinite for  $V_S \le 6V$  at room temperature and below. For  $V_S \ge 6V$ , allowable short circuit duration is 1.5ms.

Note 12: Offset voltage average drift determined by dividing the change in V<sub>OS</sub> at temperature extremes into the total temperature change.

www.trimmer.ru

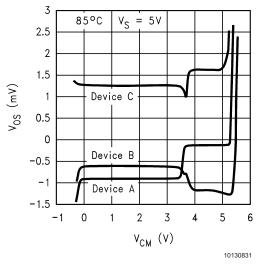

#### **Typical Performance Charateristics** Vos Distribution 20 $V_{S}$ = 5V 18 N = 5700 samples 16 Relative Frequency (%) $\sigma$ = 0.69 mV 14 12 10 8 6 4 2 0 -3 -2 0 2 3 -4 -1 1 $V_{OS}$ (mV) 101308A2 $V_{\text{OS}}$ vs. $V_{\text{CM}}$ for 3 Representative Units 2 -40°C $V_{S} = 5V$ 1.5 1 Device C $\mathfrak{S}$ 0.5 V<sub>0S</sub> 0 -0.5 Device B -1 Device A -1.5 2 3 -1 0 1 4 5 6 $V_{CM}$ (V) 10130829 $V_{\rm OS}$ vs. $V_{\rm S}$ for 3 Representative Units 1.5 DEVICE C 1

$V_{\text{OS}}$  vs.  $V_{\text{CM}}$  for 3 Representative Units

LM8272 Dual

LM8272 Dual

7

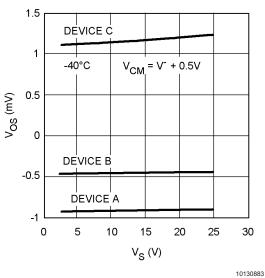

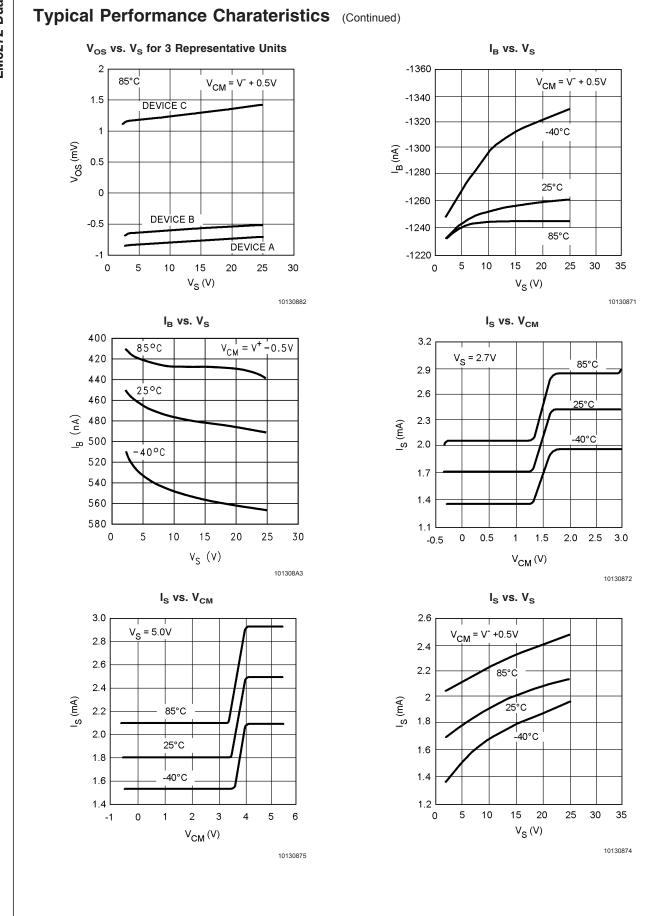

### Typical Performance Charateristics (Continued)

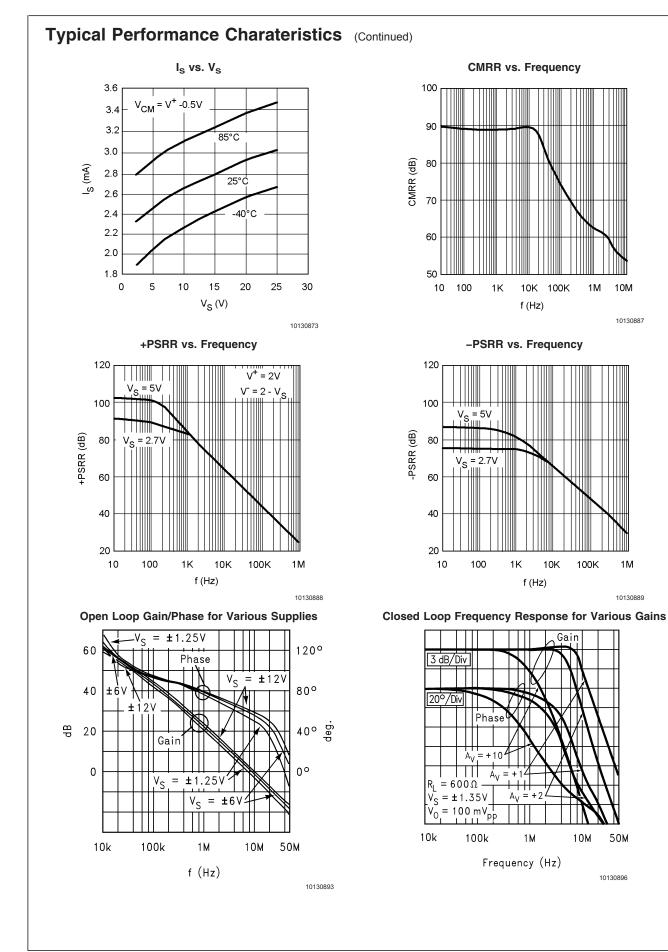

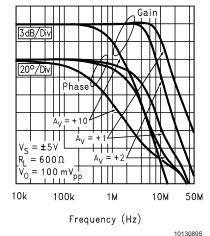

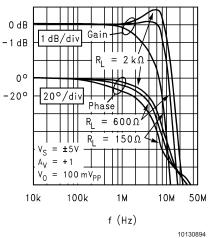

**Closed Loop Frequency Response for Various Gains**

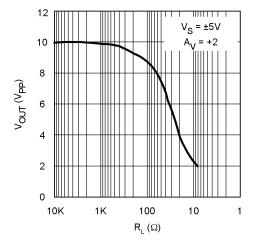

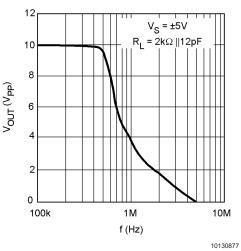

Closed Loop Small Signal Frequency Response for Various C<sub>L</sub>

10130876

Closed Loop Frequency Response for Various Gains  $\rm R_L$

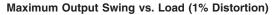

Maximum Output Swing vs. Frequency (1% Distortion)

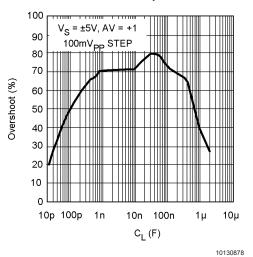

Overshoot vs. Cap Load

### Typical Performance Charateristics (Continued)

10130879

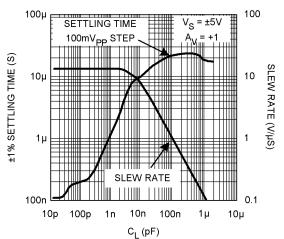

#### Settling Time (±1%) & Slew Rate vs. Cap Load

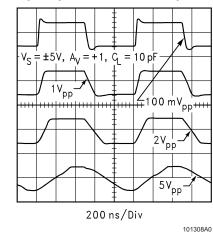

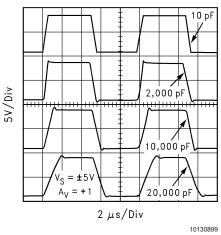

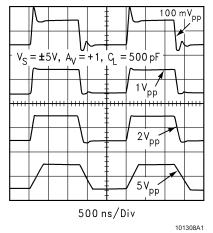

Step Response for Various Amplitudes

LM8272 Dual

V<sub>OUT</sub> from V<sup>-</sup> vs. I<sub>SINK</sub> 10V  $= \pm 5V$ ٧<sub>S</sub>  $V_{ID} =$ -200 mV 1V  $V_{OUT} \mbox{ from } V^{-} \ (V)$ 100m +85°C 10m 40°C 1m  $10\mu$   $100\mu$  1m 10m 100m  $1\mu$ I<sub>SINK</sub> (A) 10130897

Step Response for Various Amplitudes

## Typical Performance Charateristics (Continued)

#### THD+N vs. Input Amplitude for Various Frequency

Crosstalk Rejection vs. Frequency

Closed Loop Output Impedance vs. Frequency

10130885

10130892

LM8272 Dual

### **Application Notes**

## BLOCK DIAGRAM AND OPEATIONAL DESCRIPTION A) INPUT STAGE:

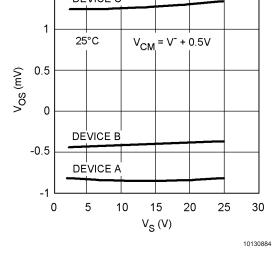

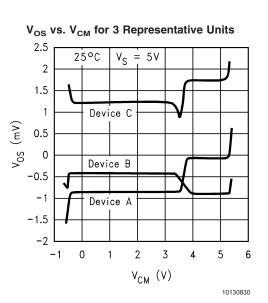

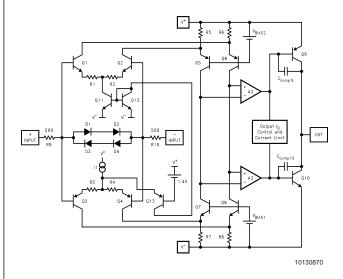

As can be seen from the simplified schematic in Figure 1, the input stage consists of two distinct differential pairs (Q1-Q2 and Q3-Q4) in order to accommodate the full Rail-to-Rail input common mode voltage range. The voltage drop across R5, R6, R7 and R8 is kept to less than 200mV in order to allow the input to exceed the supply rails. Q13 acts as a switch to steer current away from Q3-Q4 and into Q1-Q2, as the input increases beyond 1.4 of V<sup>+</sup>. This in turn shifts the signal path from the bottom stage differential pair to the top one and causes a subsequent increase in the supply current. In transitioning from one stage to another, certain input stage parameters ( $V_{OS}$ ,  $I_b$ ,  $I_{OS}$ ,  $e_n$ , and  $i_n$ ) are determined based on which differential pair is "on" at the time. Input Bias current, Ib, will change in value and polarity as the input crosses the transition region. In addition, parameter such as PSRR and CMRR which involve the input offset voltage will also be effected by changes in  $V_{CM}$  across the differential pair transition region. www.timmer.ru

FIGURE 1. Simplified Schematic Diagram

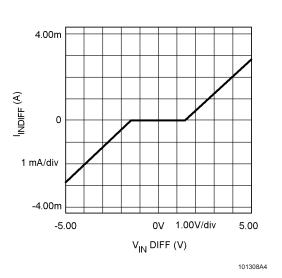

The input stage is protected with the combination of R9-R10 and D1, D2, D3 and D4 against differential input overvoltages. This fault condition could otherwise harm the differential pairs or cause offset voltage shift in case of prolonged over voltage. As shown in *Figure 2*, if this voltage reaches approximately  $\pm 1.4$ V at 25°C, the diodes turn on and current flow is limited by the internal series resistors (R9 and R10). The Absolute Maximum Rating of  $\pm 10$ V differential on V<sub>IN</sub> still needs to be observed. With temperature variation, the point were the diodes turn on will change at the rate of 5mV/°C

#### FIGURE 2. Input Stage Current vs. Differential Input Voltage

#### B) OUTPUT STAGE:

www.trimmer.ru

The output stage (see *Figure 1*) is comprised of complimentary NPN and PNP common-emitter stages to permit voltage swing to within a V<sub>ce(sat)</sub> of either supply rail. Q9 supplies the sourcing and Q10 supplies the sinking current load. Output current limiting is achieved by limiting the V<sub>ce</sub> of Q9 and Q10; using this approach to current limiting, alleviates the draw back to the conventional scheme which requires one V<sub>be</sub> reduction in output swing.

The frequency compensation circuit includes Miller capacitors from collector to base of each output transistor (see Figure 1,  $C_{comp9}$  and  $C_{comp10}$ ). At light capacitive loads, the high frequency gain of the output transistors is high, and the Miller effect increases the effective value of the capacitors thereby stabilizing the Op Amp. Large capacitive loads greatly decrease the high frequency gain of the output transistors thus lowering the effective internal Miller capacitance - the internal pole frequency increases at the same time a low frequency pole is created at the Op Amp output due to the large load capacitor. In this fashion, the internal dominant pole compensation, which works by reducing the loop gain to less than 0dB when the phase shift around the feedback loop is more than 180°, varies with the amount of capacitive load and becomes less dominant when the load capacitor has increased enough. Hence the Op Amp is very stable even at high values of load capacitance resulting in the uncharacteristic feature of stability under all capacitive loads.

#### C) OUTPUT VOLTAGE SWING CLOSE TO V-:

The LM8272's output stage design allows voltage swings to within millivolts of either supply rail for maximum flexibility and improved useful range. Because of this design architecture, as can be seen from *Figure 1* diagram, with Output approaching either supply rail, either Q9 or Q10 Collector-Base junction reverse bias will decrease. With output less than a V<sub>be</sub> from either rail, the corresponding output transistor operates near saturation. In this mode of operation, the transistor will exhibit higher junction capacitance and lower f<sub>t</sub> which will reduce Phase Margin. With the Noise Gain (NG = 1 + Rf/Rg, Rf & Rg are external gain setting resistors) of 2 or higher, there is sufficient Phase Margin that this reduction (in Phase Margin) is of no consequence. However, with lower

#### Application Notes (Continued)

Noise Gain (<2) and with less than 150 mV voltage to the supply rail, if the output loading is light, the Phase Margin reduction could result in unwanted oscillations.

In the case of the LM8272, due to inherent architectural specifics, the oscillation occurs only with respect to Q10 when output swings to within 150mV of V<sup>-</sup>. However, if Q10 collector current is larger than its idle value of a few microamps, the Phase Margin loss becomes insignificant. In this case, 300µA is the required Q10 collector current to remedy this situation. Therefore, when all the aforementioned critical conditions are present at the same time (NG < 2, V<sub>OUT</sub> < 150mV from supply rails, & output load is light) it is possible to ensure stability by adding a load resistor to the output to provide the necessary Q10 minimum Collector Current (300µA).

For 12V (or  $\pm 6V$ ) operation, for example, add a 39k $\Omega$  resistor from the output to V<sup>+</sup> to cause 300µA output sinking current and ensure stability. This is equivalent to about 15% increase in total quiescent power dissipation.

#### DRIVING CAPACTIVE LOADS:

The LM8272 is specifically designed to drive unlimited capacitive loads without oscillations (see Settling Time and Overshoot vs. Cap Load plots in the typical performance characteristics section). In addition, the output current handling capability of the device allows for good slewing characteristics even with large capacitive loads (Settling Time and Slew Rate vs. Cap Load plot). The combination of these features is ideal for applications such as TFT flat panel buffers, A/D converter input amplifiers, etc.

However, as in most Op Amps, addition of a series isolation resistor between the Op Amp and the capacitive load improves the settling and overshoot performance.

Output current drive is an important parameter when driving capacitive loads. This parameter will determine how fast the output voltage can change. Referring to the Settling Time and Slew Rate vs. Cap Load plots (typical performance characteristics section), two distinct regions can be identified. Below about 10,000pF, the output Slew Rate is solely determined by the Op Amp's compensation capacitor value and available current into that capacitor. Beyond 10nF, the Slew Rate is determined by the Op Amp's available output current. An estimate of positive and negative slew rates for loads larger than 100nF can be made by dividing the short circuit current value by the capacitor.

#### ESTIMATING THE OUTPUT VOLTAGE SWING

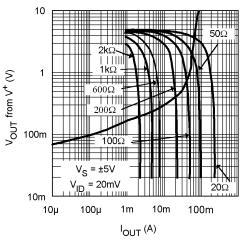

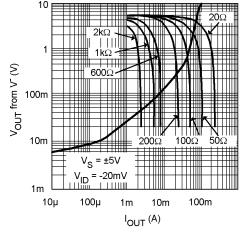

It is important to keep in mind that the steady state output current will be less than the current available when there is an input overdrive present. For steady state conditions, *Figure 3* and *Figure 4* plots can be used to predict the output swing. These plots also show several load lines correspond-

ing to loads tied between the output and ground. In each case, the intersection of the device plot at the appropriate temperature with the load line would be the typical output swing possible for that load. For example, a 600 $\Omega$  load can accommodate an output swing to within 100mV of V<sup>-</sup> and to 250mV of V<sup>+</sup> (V<sub>S</sub> = ±5V) corresponding to a typical 9.65V<sub>PP</sub> unclipped swing.

10130890

FIGURE 3. Steady State Output Sourcing Characteristics with Load Lines

10130891

FIGURE 4. Steady State Output Sinking Characteristics with Load Lines

### Application Notes (Continued)

## OUTPUT SHORT CIRCUIT CURRENT AND DISSIPATION ISSUES:

The LM8272 output stage is designed for maximum output current capability. Even though momentary output shorts to ground and either supply can be tolerated at all operating voltages, longer lasting short conditions can cause the junction temperature to rise beyond the absolute maximum rating of the device, especially at higher supply voltage conditions. Below supply voltage of 6V, output short circuit condition can be tolerated indefinitely.

With the Op Amp tied to a load, the device power dissipation consists of the quiescent power due to the supply current flow into the device, in addition to power dissipation due to the load current. The load portion of the power itself could include an average value (due to a DC load current) and an AC component. DC load current would flow if there is an output voltage offset, or the output AC average current is non-zero, or if the Op Amp operates in a single supply application where the output is maintained somewhere in the range of linear operation. Therefore:

| $P_{total} = P_Q + P_{DC} + P_{AC}$    |                        |

|----------------------------------------|------------------------|

| $P_Q = I_S \cdot V_S$                  | Op Amp Quiescent Power |

|                                        | Dissipation            |

| $P_{DC} = I_{O} \cdot (V_{r} - V_{o})$ | DC Load Power          |

| $P_{AC}$ = See Table 1 below           | AC Load Power          |

where:

Is: Supply Current

$V_{S}$ : Total Supply Voltage (V<sup>+</sup> - V<sup>-</sup>)

V<sub>O</sub>: Average Output Voltage

$V_r$ : V<sup>+</sup> for sourcing and V<sup>-</sup> for sinking current

Table 1 below shows the maximum AC component of the load power dissipated by the Op Amp for standard Sinusoidal, Triangular, and Square Waveforms:

TABLE 1. Normalized AC Power Dissipated in the Output Stage for Standard Waveforms

| Sinusoidal              | Triangular              | Square                  |

|-------------------------|-------------------------|-------------------------|

| 50.7 x 10 <sup>-3</sup> | 46.9 x 10 <sup>-3</sup> | 62.5 x 10 <sup>-3</sup> |

The table entries are normalized to  $V_S^2/R_L$ . To figure out the AC load current component of power dissipation, simply multiply the table entry corresponding to the output waveform by the factor  $V_S^2/R_L$ . For example, with ±12V supplies, a 600 $\Omega$  load, and triangular waveform power dissipation in the output stage is calculated as:

$P_{AC} = (46.9 \times 10^{-3}) \cdot [24^2/600] = 45.0 \text{mW}$

#### **OTHER APPLICATION HINTS:**

The use of supply decoupling is mandatory in most applications. As with most relatively high speed/high output current Op Amps, best results are achieved when each supply line is decoupled with two capacitors; a small value ceramic capacitor (~0.01µF) placed very close to the supply lead in addition to a large value Tantalum or Aluminum (> 4.7µF). The large capacitor can be shared by more than one device if necessary. The small ceramic capacitor maintains low supply impedance at high frequencies while the large capacitor will act as the charge "bucket" for fast load current spikes at the Op Amp output. The combination of these capacitors will provide supply decoupling and will help keep the Op Amp oscillation free under any load.

#### LM8272 ADVANTAGES:

Compared to other Rail-to-Rail Input/Output devices, the LM8272 offers several advantages such as:

- Improved cross over distortion www.timmer.ru

- Nearly constant supply current throughout the output voltage swing range and close to either rail.

- Nearly constant Unity gain frequency (f<sub>u</sub>) and Phase Margin (Phi<sub>m</sub>) for all operating supplies and load conditions.

- No output phase reversal under input overload condition.